Product Summary

The EPM7128AETC100-10N is a high-density, highperformance device based on Alteras second-generation MAX architecture. Fabricated with advanced CMOS technology, the EEPROMbased EPM7128AETC100-10N operate with a 3.3-V supply voltage and provide 600 to 10,000 usable gates, ISP, pin-to-pin delays as fast as 4.5 ns, and counter speeds of up to 227.3 MHz. The EPM7128AETC100-10N in the -4, -5, -6, -7, and some -10 speed grades are compatible with the timing requirements for 33 MHz operation of the PCI Special Interest Group (PCI SIG) PCI Local Bus Specification, Revision 2.2.

Parametrics

EPM7128AETC100-10N absolute maximum ratings: (1)VCC Supply voltage With respect to ground: -0.5 to 4.6 V; (2)VI DC input voltage: -2.0 to 5.75 V; (3)IOUT DC output current, per pin: -25 to 25 mA; (4)TSTG Storage temperature No bias: -65 to 150 ° C; (5)TA Ambient temperature Under bias: -65 to 135 ° C; (6)TJ Junction temperature BGA, FineLine BGA, PQFP, and TQFP packages, under bias: 135 ° C; (7)tR Input rise time: 40 ns; (8)tF Input fall time: 40 ns.

Features

EPM7128AETC100-10N features: (1)High-performance 3.3-V EEPROM-based programmable logic devices (PLDs)built on second-generation Multiple Array MatriX (MAX)architecture; (2)3.3-V in-system programmability (ISP)through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG)interface with advanced pin-locking capability; (3)MAX 7000AE device in-system programmability (ISP)circuitry compliant with IEEE Std. 1532; (4)EPM7128A and EPM7256A device ISP circuitry compatible with IEEE Std. 1532; (5)Built-in boundary-scan test (BST)circuitry compliant with IEEE Std. 1149.1; (6)Supports JEDEC Jam Standard Test and Programming Language (STAPL)JESD-71; (7)Enhanced ISP features; (8)Enhanced ISP algorithm for faster programming (excluding EPM7128A and EPM7256A devices); (9)ISP_Done bit to ensure complete programming (excluding EPM7128A and EPM7256A devices); (10)Pull-up resistor on I/O pins during in-system programming; (11)Pin-compatible with the popular 5.0-V MAX 7000S devices; (12)High-density PLDs ranging from 600 to 10,000 usable gates; (13)Extended temperature range.

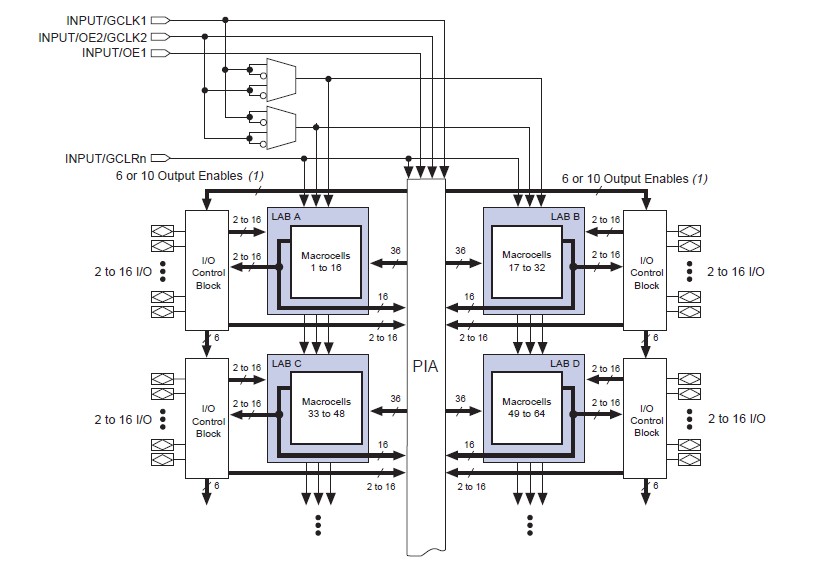

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

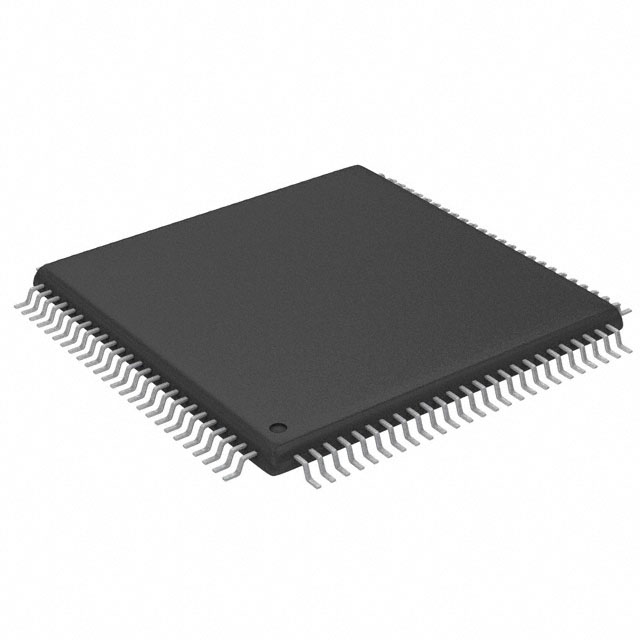

EPM7128AETC100-10N |

|

IC MAX 7000 CPLD 128 100-TQFP |

Data Sheet |

|

|

||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|

EPM7032AE |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

EPM7032AELC44-10 |

|

IC MAX 7000 CPLD 32 44-PLCC |

Data Sheet |

|

|

||||||

|

EPM7032AELC44-10N |

|

IC MAX 7000 CPLD 32 44-PLCC |

Data Sheet |

|

|

||||||

|

EPM7032AELC44-4 |

|

IC MAX 7000 CPLD 32 44-PLCC |

Data Sheet |

|

|

||||||

|

EPM7032AELC44-4N |

|

IC MAX 7000 CPLD 32 44-PLCC |

Data Sheet |

|

|

||||||

|

EPM7032AELC44-7 |

|

IC MAX 7000 CPLD 32 44-PLCC |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))